D鎖存器

前面所講的組合邏輯電路有個特點,就是任何時候的輸出僅僅只由同一時刻的輸入所決定,而我們接下來涉及的時序邏輯電路呢,可不僅僅是那麽簡單了。

它的輸出不但由輸入量控制,而且與它在上一個時刻的輸出有關。

【至於所謂的 “上一個時刻” 到底是什麽時刻這裡我們先不管】。

時序邏輯電路最重要的組成部分是觸發器,觸發器有很多種,我們就介紹比較普遍的D觸發器即可。

為了深入了解觸發器,我們從構成觸發器的鎖存器開始介紹咯。

1:用與非門構成的SR鎖存器

鎖存器是何許人物也?

鎖存器是能保存上一刻的輸入的一個小電路。

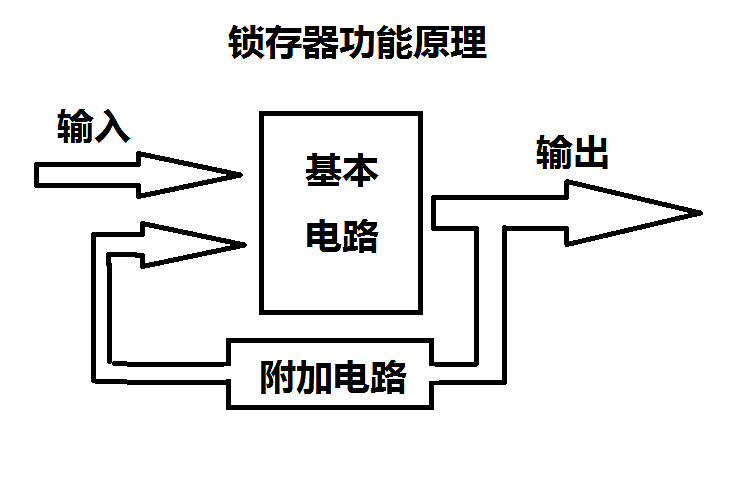

怎麽保存呢?基本思路就是:把輸出連接埠想辦法連回輸入連接埠就ok啦。

那麽基本思路就是這樣:

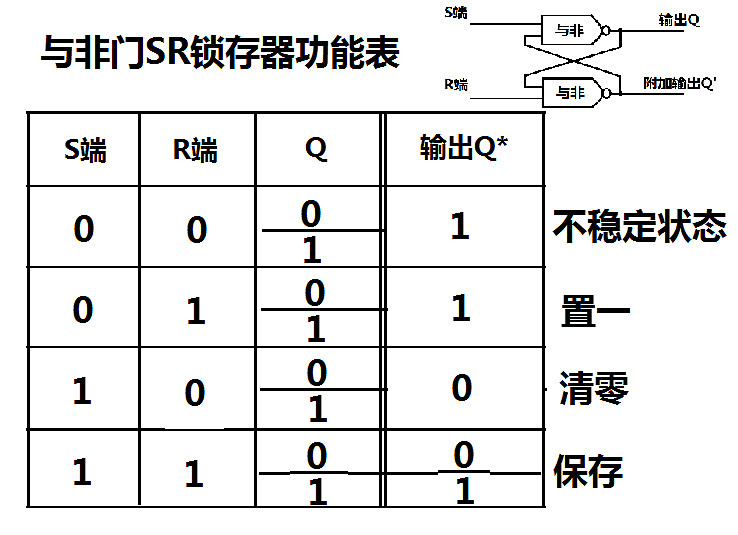

在此基礎上,用與非門構成的SR鎖存器橫空出世了。

這個電路僅僅由兩個與非門構成,是相當的簡單的。

如圖所示:

至於為什麽用SR這個名稱,因為這兩端各有置一(set)的功能和清零(reset)的功能。

現在來分析這個電路。

為了讓說明清楚些,我將上一刻的輸出記為Q,此刻的輸出記為Q*。

這個電路不外乎以下4種情況:

先看前三種,我們一步步分析。

接下來就是最重要的第四種情況了,Q*=Q的情況,此時Q*=Q。

最後我們有如下的功能表給大家作參考:

來源:遊俠網